Crooks Threaten To Leak 3 Billion Personal Records 'Stolen From Background Firm'

Read more of this story at Slashdot.

Read more of this story at Slashdot.

Intel this morning is lifting the lid on some of the finer architectural and technical details about its upcoming Lunar Lake SoC – the chip that will be the next generation of Core Ultra mobile processors. Once again holding one of their increasingly regular Tech Tour events for media and analysts, Intel this time set up shop in Taipei just before the beginning of Computex 2024. During the Tech Tour, Intel disclosed numerous facets of Lunar Lake, including their new P-Core design codenamed Lion Cove and a new wave of E-cores that are a bit more like Meteor Lake's pioneering Low Power Island E-Cores. Also disclosed was the Intel NPU 4, which Intel claims delivers up to 48 TOPS, surpassing Microsoft's Copilot+ requirements for the new age of AI PCs.

Intel's Lunar Lake represents a strategic evolution in their mobile SoC lineup, building on their Meteor Lake launch last year, focusing on enhancing power efficiency and optimizing performance across the board. Lunar Lake dynamically allocates tasks to efficient cores (E-cores) or performance cores (P-cores) based on workload demands by leveraging advanced scheduling mechanisms, which are assigned to ensure optimal power usage and performance. Still, once again, Intel Thread Director, along with Windows 11, plays a pivotal role in this process, guiding the OS scheduler to make real-time adjustments that balance efficiency with computational power depending on the intensity of the workload.

Closing out the last of the major PC-focused keynotes at Computex 2024 this evening, we have Intel. The long-reigning leader of the PC CPU market, Intel is in the middle of executing its plans to get back on track on both the manufacturing and chip design aspects of the business. Tonight’s keynote, being helmed by the highly-animated Pat Gelsinger, is titled “Bringing AI Everywhere.” And, like so many other Computex presentations and announcements this week, AI hardware is going to play a big part, as Intel outlines a full stack of products for client and server computing.

Of the four great PC chip vendors at the show, Intel has been the most up-front about what to expect from their hour-long presentation. The company’s Computex 2024 page already outlines their four major topics: AI PCs, Xeon 6 Processors, Gaudi AI accelerators, and Intel’s OpenVINO software ecosystem.

On the consumer hardware front, the company set the table with a significant teaser earlier this month about their forthcoming mobile PC SoC, Lunar Lake. The next generation of Core Ultra processors, Intel is touting significant energy efficiency gains for the mobile-focused chip, with new architectures driving their Performance and Efficiency CPU cores, Xe2 GPU, and a much faster 45+ TOPS (INT8) NPU. While the Lunar Lake announcement is coming relatively soon after the Meteor Lake launch, Intel has made it clear that it’s not going to hold back on shipping future products; they are looking to make up for lost time. Still, Lunar Lake devices are not expected to hit retail shelves until Q4 of this year, so this announcement is coming months in advance of the hardware itself.

On the server front, Intel has been publicly prepping for the launch of a new generation of Xeons with the Xeon 6 platform. The most notable part of this being the release of the company’s first Efficiency-core Xeon, Sierra Forest. Sierra Forest is set to be the first Xeon 6 chip out the door this year, and will offer up to 288 E cores on a single chip, allowing Intel to tap into the many (many) core CPU markets that AMD and Arm-based rivals have been unopposed at thus far.

Finally, the company has fully pivoted its server AI accelerator strategy to its Gaudi accelerators. Gaudi 3 was introduced back in April, and while it isn’t expected to go toe-to-toe with NVIDIA’s top accelerators in every workload, Intel is betting that they can beat NVIDIA on critical workloads, all while undercutting them significantly in pricing. The first Gaudi 3 parts are set to be released in the second half of this year, so hopefully we’ll be hearing a bit more about Intel’s plans as part of their keynote.

As always, the AnandTech crew is live and in person to catch this final Computex keynote. So please come join us at 8:00pm PT / 11:00pm ET / 03:00 UTC to get all the details.

Alors que la conférence de Gigabyte tournait autour de l'IA, quelques cartes mères étaient exposées sur le côté. Le chipset était masqué, mais le petit logo Intel sur le socket nous laissait deviner que nous avions sous les yeux les futurs cartes mères à destination des futurs processeurs ARROW LAKE-S, donc très probablement les Z890 dont les noms avaient leakés il y a quelques jours. Voici donc les « NEXT GEN » Z AORUS ULTRA, AORUS PRO X USB4, Z AORUS ELITE X ICE, Z AORUS ELITE WIFI 7, Z AORUS MASTER, Z AERO G et bien entendu la sublime TACHYON ICE aui a eu droit à sa propre news. […]

Lire la suiteRead more of this story at Slashdot.

Read more of this story at Slashdot.

Read more of this story at Slashdot.

Read more of this story at Slashdot.

Read more of this story at Slashdot.

Read more of this story at Slashdot.

Read more of this story at Slashdot.

Read more of this story at Slashdot.

Minimachines.net en partenariat avec TopAchat.com

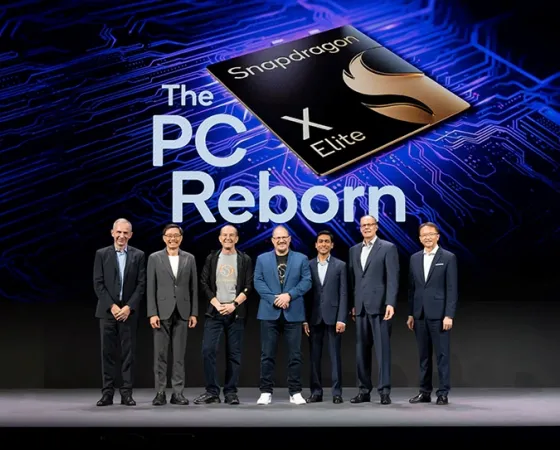

Les Snapdragon X Plus et Snapdragon X Elite sont certes lancés sur des plateformes mobiles mais Qualcomm n’entend pas les réserver au monde des portables et des tablettes.

Le PDG de Qualcomm, Cristiano Amon, entend bien que son offre de SoC ARM intègre tout type de PC sous Windows. On parle donc de solutions classiques même si je ne suis pas certain que le format tour leur soit le plus accessible. Pour d’évidentes question d’évolutivité moins évidente pour les SoC de ce type que pour une puce x86 AMD ou Intel montée sur un socket, le format apparait comme plus fermé. Mais pour des MiniPC, des All In One et autres solutions type Clé-PC ou autres intégrations, les puces de la marque auront toute leur place.

Pour le format MiniPC ou le All-In-One par exemple, il est bien évident que ce type de puce mobile a autant d’intérêt que les solutions x86 classiques. On a déjà vu un premier MiniPC sous SoC Snapdragon X avec le kit de développement de la marque présenté lors de l’annonce des puces. Il est parfaitement envisageable d’imaginer des engins de ce type être proposés rapidement.

Reste à convaincre les marques partenaires d’un côté et les clients de l’autre. Sur ces segments des arguments de performances comptent mais ils ne sont pas les seuls. Le tarif est un point essentiel de l’équation. On a vu avec la première salve de portables équipés de ces puces que les prix demandés par les différents acteurs étaient au dessus des machines plus classiquement sous puces AMD et Intel. On imagine mal des particuliers comme des entreprises se pencher sur des minimachines de ce genre si elles se positionnent au dessus de la concurrence niveau tarif.

Si Qualcomm dit à ses partenaires que la porte est ouverte, c’est peut être pour tenter d’intéresser du monde vers ces formats, preuve que pour le moment cela ne se bouscule pas vraiment de ce côté là.

Qualcomm veut glisser ses Snapdragon X dans tous les PC © MiniMachines.net. 2024.

Arm a visiblement de grosses ambitions renouvelées pour le marché du PC, qui lui échappe, c’est vrai, depuis bien longtemps. C’est Intel et le processeur x86 qui y font la loi depuis des décennies. Mais après plusieurs tentatives sans succès d’accoupler Windows et Arm, le vent pourrait bien être ame...

Arm a visiblement de grosses ambitions renouvelées pour le marché du PC, qui lui échappe, c’est vrai, depuis bien longtemps. C’est Intel et le processeur x86 qui y font la loi depuis des décennies. Mais après plusieurs tentatives sans succès d’accoupler Windows et Arm, le vent pourrait bien être ame...

With AMD’s Zen 5 CPU architecture only a month away from its first product releases, the new CPU architecture was placed front and center for AMD’s prime Computex 2024 keynote. Outlining how Zen 5 will lead to improved products across AMD’s entire portfolio, the company laid out their product plans for the full triad: mobile, desktop, and servers. And while server chips will be the last parts to be released, AMD also saved the best for last by showcasing a 192 core EPYC “Turin” chip.

Turin is the catch-all codename for AMD’s Zen 5-based EPYC server processors – what will presumably be the EPYC 9005 series. The company has previously disclosed the name in earnings calls and other investor functions, outlining that the chip was already sampling to customers and that the silicon was “looking great.”

The Computex reveal, in turn, is the first time that the silicon has been shown off to the public. And with it, we’ve received the first official confirmation of the chip’s specifications. With SKUs up to 192 CPU cores, it’s going to be a monster of an x86 CPU.

| AMD EPYC CPU Generations | ||||

| AnandTech | EPYC 5th Gen (Turin, Z5c) |

EPYC 9704 (Bergamo) |

EPYC 9004 (Genoa) |

EPYC 7003 (Milan) |

| CPU Architecture | Zen 5c | Zen 4c | Zen 4 | Zen 3 |

| Max CPU Cores | 192 | 128 | 96 | 64 |

| Memory Channels | 12 x DDR5 | 12 x DDR5 | 12 x DDR5 | 8 x DDR4 |

| PCIe Lanes | 128 x 5.0 | 128 x 5.0 | 128 x 5.0 | 128 x 4.0 |

| L3 Cache | ? | 256MB | 384MB | 256MB |

| Max TDP | 360W? | 360W | 400W | 280W |

| Socket | SP5 | SP5 | SP5 | SP3 |

| Manufacturing Process |

CCD: TSMC N3 IOD:TSMC N6 |

CCD: TSMC N5 IOD: TSMC N6 |

CCD: TSMC N5 IOD: TSMC N6 |

CCD: TSMC N7 IOD: GloFo 14nm |

| Release Date | H2'2024 | 06/2023 | 11/2022 | 03/2021 |

Though only a brief tease, AMD’s Turin showcase did confirm a few, long-suspected details about the platform. AMD will once again be using their socket SP5 platform for Turin processors, which means the chips are drop-in compatible with EPYC 9004 Genoa (and Bergamo). The reuse of SP5 means that customers and server vendors can immediately swap out chips without having to build/deploy whole new systems. It also means that Turin will have the same base memory and I/O options as the EPYC 9004 series: 12 channels of DDR5 memory, and 128 PCIe 5.0 lanes.

In terms of power consumption, existing SP5 processors top out at 400 Watts, and we’d expect the same for these new, socket-compatible chips.

As for the Turin chip itself, while AMD is not going into further detail on its configuration, all signs point to this being a Zen 5c configuration – that is, built using CCDs designed around AMD’s compact Zen 5 core configuration. This would make the Turin chip on display the successor to Bergamo (EPYC 9704), which was AMD’s first compact core server processor, using Zen 4c cores. AMD’s compact CPU cores generally trade off per-core performance in favor of allowing more CPU cores overall, with lower clockspeed limits (by design) and less cache memory throughout the chip.

According to AMD, the CCDs on this chip were fabbed on a 3nm process (undoubtedly TSMC’s), with AMD apparently looking to take advantage of the densest process available in order to maximize the number of CPU cores the can place on a single chip. Even then, the CCDs featured here are quite sizable, and while we’re waiting for official die size numbers, it would come as no surprise if Zen 5’s higher transistor count more than offset the space savings of moving to 3nm. Still, AMD has been able to squeeze 12 CCDs on to the chip – 4 more than Bergamo – which is what’s allowing them to offer 192 CPU cores instead of 128 as in the last generation.

Meanwhile, the IOD is confirmed to be produced on 6nm. Judging from that fact, the pictures, and what AMD’s doing with their Zen 5 desktop products, there is a very good chance that AMD is using either the same or a very similar IOD as on Genoa/Bergamo. Which goes hand-in-hand with the socket/platform at the other end of the chip staying the same.

AMD’s brief teaser did not discuss at all any other Turin configurations. So there is nothing else official to share about Turin chips built using full-sized Zen 5 CPU cores. With that said, we know that the full-fat cores going into the Ryzen 9000 desktop series pack 8 cores to a CCD and are being fabbed on a 4nm process – not 3nm – so that strongly implies that EPYC Zen 5 CCDs will be the same. Which, if that pans out, means that Turin chips using high performance cores will max out at 96 cores, the same as Genoa.

Hardware configurations aside, AMD also showcased a couple of benchmarks, pitting the new EPYC chips against Intel’s Xeons. As you’d expect in a keynote teaser, AMD was winning handily. Though it is interesting to note that the chips benchmarked were all 128 core Turins, rather than on the 192 core model being shown off today.

AMD will be shipping EPYC Turin in the second half of this year. More details on the chips and configurations will follow once AMD gets closer to the EPYC launch.